Wang Quan 1, 2, 3 Soleil océan, Shao Zhiyang 3, 1, 2 super cheval

(1 AVIC Xi'an Institut de Technologie de l'informatique de l'industrie aérospatiale, Xi'an 710068;

2. Laboratoire clé d'ASIC et systčme de conception Micro Aviation Technology, Xi'an 710068; 3. Xi'an Xiang Teng Microelectronics Technology Co., Ltd, Xi'an 710068)

Avec la complexité croissante de l'intégration du systčme d'aviation, comment surveiller efficacement le comportement des données de bus, l'analyse des données en temps réel, le diagnostic de défaut et de localisation est une question importante pour le systčme avioniques. Analyseur de bus ARINC659 proposé basé sur le développement de la conception FPGA, la principale réalisation de surveillance des données de bus ARINC659, l'échantillonnage, le stockage et le test d'injection de défaut, le bus de données peut ętre déclenchée via l'interface de communication et d'analyse en temps réel pour évaluer le comportement du bus, le bus de données est ARINC659 analyse en temps réel fournit une méthodes de test complčtes et fiables.

ARINC659, le suivi, l'analyse, la capture

CLC: TN913

A

DOI: 10,16157 / j.issn.0258-7998.2016.10.038

format de citation chinois: Wang Quan, océan Sun, Shao Zhiyang, etc. conception de l'analyseur de bus et une ARINC659 mise en uvre basée sur FPGA Technologie électronique, 2016,42 (10): 146-148,152.

Anglais format de citation: Wang Quan, Sun Haiyang, Shao Zhiyang, et al. Conception A et la mise en uvre de l'analyseur de protocole ARINC659 basé sur FPGA .Application Technique électronique, 2016,42 (10): 146-148,152.

0 introduction

systčmes d'avionique développement d'intégration et d'améliorer constamment, la sécurité, la tolérance aux pannes, les exigences du systčme en temps réel devient de plus en plus. ligne de bus de fond de panier systčme avionique entre chaque module (LRM) partie de clé indispensable de transmission de données peut ętre remplaçable. Augmenter la complexité de l'intégration du systčme d'aviation de sorte que le moniteur de bus de données comment mener efficacement l'analyse des données en temps réel, le diagnostic de défaut et de localisation est devenue un problčme important du systčme avioniques. Tigong peut déclencher une surveillance transitoire et l'analyse de l'état de la communication entre le systčme LRM sera grandement améliorée avionique efficacité de la maintenance du systčme, réduire le temps de maintenance de défaillance du systčme, la mise ŕ niveau d'entretien de l'équipement et la disponibilité joueront un rôle majeur dans .

Cet article présente un systčme de bus instrument d'analyse de conception de FPGA ARINC659 basé sur bus de données peut ętre effectué de surveillance ARINC659, injection de fautes, fonctions de test de simulation.

1 Conception

1,1 mécanisme de transmission

ARINC659 est un bus série, un bus série en utilisant quatre communications par moitié communication duplex avec la vérification croisée, il réduit le matériel, d'améliorer la fiabilité. ARINC659 est composé ŕ la fois du double bus, le bus A, B a « x », « y » deux bus, chaque bus comporte une ligne d'horloge et de deux lignes de données, respectivement, chaque paire de bits de transmission de données, plein 12 par les lignes de bus.

ARINC659 tolérance de panne ŕ double bus de détection de passage, les données reçues est d'abord décodé en conséquence, transversale (AX = AY, BX = BY validité du bus de données reçu 4 et les données décodées, AX = BY, AY = BX) comparer le résultat de la comparaison de l'intégrité de la table de détermination de la validité ou de la table de disponibilité conformément ŕ l'appel de données.

initialisation de table principale du bus de commande est terminée, la commande de précodage, chaque tâche dans la configuration du systčme de la communication entre les noeuds et chaque noeud.

1.2 travaux

Comme avec d'autres modules d'analyseur bus sont montés LRM ARINC659 sur le bus, le bus 1 est appliqué dans le systčme de l'analyseur, l'analyseur et le bus de systčme autre table de commande LRM avec le męme bus, si l'analyseur de bus comme mode d'analyse, lorsque le bus d'alimentation du systčme commence la communication de données, un LRM de données sur le bus, les données de bus sur l'analyseur commence tout bus de réception, le message de données et un traitement d'analyse de message de synchronisation par le contrôle de l'hôte interface d'affichage en temps réel bus de données d'état, un analyseur de bus reçoit uniquement des données sur le bus, les données transmises sur le bus ou pas de changement, le bus ARINC 659 définit une fenętre, il ne peut y avoir qu'un seul émetteur, ou l'émetteur du bus de transmission de données de réserve , permet ŕ l'appareil de recevoir la pluralité de bus de données, la configuration de la table des commandes de configuration de bus seulement comme un analyseur d'état de réception. Analyseur de bus reçoit des données du bus par l'intermédiaire de l'émetteur-récepteur de bus et un bus de données avec une fréquence d'échantillonnage d'horloge ŕ 240 MHz, le module d'acquisition de données pour effectuer le traitement d'extrémité avant, ŕ l'analyse de protocole de bus de processeur et de faire l'analyse des données par l'état du bus de transmission Ethernet logiciel ŕ la couche d'application, les données de la couche d'application de traitement en temps réel grâce ŕ l'interface graphique affichant les informations d'état du bus. Lorsque le mode d'injection de défaut de bus comme l'analyseur, le bus d'analyseur comme un dispositif d'entrée vers le bus de données est fourni défaut de déconnexion ou de l'échec est prévu vers le bas de l'erreur de bus causes injection d'erreurs de bus .

Bus sous tension et analyseur initialisé l'initialisation du bus de puissance entičrement compatible et spécification synchronisation ARINC 659, aprčs la mise sous tension lors de l'initialisation est terminée bus de contrôle de l'état, la transmission de données en temps réel sur le bus pour le bus de données de l'hôte pour effectuer l'analyse et l'affichage.

1.3 Conception du matériel

Analyseur de bus ARINC659 est principalement composé d'un circuit d'alimentation de puissance, un circuit de remise ŕ zéro, le circuit d'émetteur-récepteur de bus, le bus de circuit de relais, une unité d'acquisition de données (FPGA et un circuit de configuration), une unité de traitement de données composé de la CPU. . Schéma-bloc de fonction de la figure 2, l'unité d'acquisition de données complčte les échantillons de fréquence de données du bus de données; les données de bus de données du processeur l'unité de traitement est responsable de la transmission de transformation et en temps réel sur le bus hôte statut de maître. Unité de traitement de données du processeur requiert une certaine mémoire du module de CPU comprend une interface PCI et Ethernet.

Le circuit d'alimentation est un module d'alimentation électrique du systčme, la puce de l'ensemble du systčme pour fournir divers tension de fonctionnement souhaitée.

remet ŕ zéro du circuit ŕ réarmement manuel, la mise sous tension, Init trois sortes de façon de réinitialisations mécanisme de remise ŕ zéro du systčme souple.

circuit récepteur émetteur-récepteur de bus est responsable des données, le circuit comprenant quatre bus indépendants, chaque bus émetteur-récepteur reçoit bus de données seule façon, la plupart des 659 systčmes actuels sur le marché ont adopté le niveau de BTL, l'émetteur-récepteur utilise le TTL transitions de niveau BTL sur la fonction d'émetteur-récepteur de bus, la conception de commande BIUy AX, l'émetteur-récepteur permet de recevoir bus BX, AY de commande BIUx, en recevant l'émetteur-récepteur permet bus.

Le circuit de relais est un échec complet du circuit d'injection changement d'état du bus, l'état du relais commandé par le contrôleur FPGA.

L'unité d'acquisition de données est une partie essentielle d'un analyseur de bus, composée principalement d'une configuration de FPGA et une mise en oeuvre de circuit périphérique, le module FPGA d'acquisition de base se termine principalement les fonctions suivantes:

(1) l'unité d'échantillonnage: unité d'échantillonnage d'horloge ŕ haute fréquence 659 échantillonne le bus de données, depuis le bus 659 en utilisant une grande commande de courant, le bus de données peut ętre bavure relativement grande, de sorte que la fréquence d'échantillonnage est relativement élevée, la conception de la fréquence d'échantillonnage est la fréquence de fonctionnement du bus 8 temps d'échantillonnage pour l'intégrité des données. unité d'échantillonnage en temps réel d'échantillonnage du bus de données, et une échelle locale jouant les données échantillonnées aux conventions de format de sortie.

(2) le circuit de filtrage: des données échantillonnées est d'abord récupération de données et d'ébavurage.

(3) des moyens de détection: des moyens pour détecter les données filtrées est déterminée une premičre information de synchronisation ou de données, si l'information de synchronisation est transmise directement l'unité de commande de surveillance, la validation des données, la correction des données si les données sont décodées ŕ un segment de données seront reçues en fonction de la table de disponibilité du test d'intégrité ou d'une table en fonction de la validité reçu du bus de données 4 et le résultat de la comparaison de la traversée de détermination, aprčs que les données d'état de contrôle de vérification des données épissées ensemble en 32 bits (un mot) puis transmises ŕ la surveillance l'unité de commande.

(4) le suivi de l'unité de contrôle: l'unité de commande de suivi pour mettre en oeuvre des messages de données, la communication de données en temps réel entre l'unité centrale et l'unité de traitement de données du message de synchronisation, l'unité d'échantillonnage unité de détection permettra de recueillir et de vérifier l'état des données de contrôle transmises ŕ l'unité centrale de traitement dans le traitement en temps réel unité module, et un bus de commande de relais circuit d'injection de l'injection de défaut "0", "1", le défaut de déconnexion.

(5) Host Interface: Le taux de transfert de bus de données, la conception actuelle utilise 33 MHz × 32 bits des interfaces de bus PCI, l'interface de bus PCI intégré directement Xlinx PCI LogiCORE, qui est conçu pour ętre entičrement compatible avec 33 MHz × spécification de protocole de bus de 32 bits, les données de la CPU l'unité de traitement est complété par la communication de données ŕ débit élevé avec le module d'acquisition de registre de DPRAM associé .

les données de la CPU unité de traitement est un processeur central ŕ travers l'analyseur, le principal mode de traitement et le mode de déclenchement de capture, aprčs traitement des données par les différents modes de données Ethernet au logiciel de couche d'application aux contraintes de la couche d'application.

1.4 Conception du systčme logiciel

plate-forme logicielle de l'analyseur de bus ARINC659: hôte en utilisant PC, le systčme d'accueil met en uvre les communications analyseur pilotes logiciels par l'analyseur, le package API, un éditeur de langage de description de trame via l'interface Ethernet et un logiciel d'application PC est transmise logiciel. 3 l'architecture logicielle représentée sur la figure.

Le logiciel principal d'application fournit une interface simple, intuitive grâce ŕ un logiciel d'application GUI unifiée pour contrôler son travail pour fournir 659 l'analyse des données, les données de surveillance 659, capture de données 659, 659 capacités d'injection de défaut de bus.

(1) Analyse des données: 659 Fil message de synchronisation de vitesse et le message de données recevant fonction 659; 659 pour analyser les données en temps réel et affichées dans un cadencement synchronisé.

(2) la fonction de surveillance des données: les données statistiques de l'état reçu, le trafic de données de surveillance, le suivi et l'analyse des données d'état d'erreur, les statistiques d'erreur, s'il n'y a pas de liaison de données fiables ou ébarbures bus, les numéros de version correspondent, la commutation de cadre reçu les données non corrigibles, validation d'émission correspondance; message de données d'analyse est déterminé par le message d'erreur de synchronisation si les impulsions de synchronisation pour atteindre l'état en temps réel de l'analyse de traces de bus de systčme.

(3) les fonctions de saisie de données: pour fournir la saisie des données en temps réel en ligne et de déclencher la capture, les enregistrements sont stockés données sur le stockage de données sur le disque dur hôte est mis en uvre par le logiciel.

(4) Défaut Bus fonction d'injection: injection de défaut de bus est « 0 », le défaut est injecté par l'intermédiaire du bus de commande Chaque relais conçu pour réaliser trois états « 1 », la déconnexion, pour chaque groupe de signaux, en plus de particuliers autre que l'injection de signal d'erreur, comprenant en outre un cas oů l'adhérence les unes aux autres, un total de trois types d'adhérences: CK adhérence et D0, D1 et D0 adhérence de chaque groupe, CK, l'adhérence D0, D1. Par défaut, tous les signaux ne sont pas la faute d'injection, dans l'état normal de la communication. Interface conception représentée sur la. Figure 4 que l'injection de panne logicielle.

Logiciel pilote et logiciel d'application sont transmises sous forme d'un logiciel d'interface de communication, le pilote du logiciel systčme qui comprend une unité centrale de traitement, le pilote d'interface PCI, pilote Ethernet et logiciels de communication, les pilotes de logiciel fournit un systčme de contrôle module d'acquisition de l'unité centrale, le service d'interruption, l'état des rapports, différents modes de traitement de données et d'autres services d'application, un pilote fournit une analyse de données Ethernet interface Ethernet, le logiciel API, la communication entre l'interface PCI initialisation du pilote d'interface PCI terminée, et un module d'acquisition de bus CPU, un bus logiciel de communication de transfert de données .

un logiciel de transmission que le logiciel sous-jacent de l'analyseur pour terminer la préparation du bus principal et une table de commande de transfert de données du bus. ARINC659 complčtement bus table d'événements récurrents bus basé sur le bus de commande 659, la commande de langage de description de trame est utilisé pour définir des trames de données de fonctionnement de bus ARINC659 chaque fenętre, la longueur de la fenętre, les paramčtres de commande.

2 vérification fonctionnelle

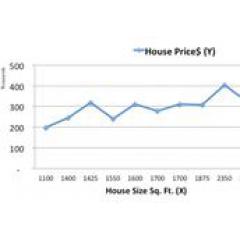

environnement de construction selon la. figure 1 forme de réalisation, chaque noeud sur le systčme de bus est injection de faute d'états différents, dans l'enregistrement en temps réel du bus par l'intermédiaire d'un analyseur de bus, de capture, de surveiller et d'analyser . Analyseur de bus initié selon une commande d'un hôte, ou ŕ des données d'arręt de collecte différents modes, le systčme utilise la fréquence d'échantillonnage de 240 MHz sur les données de bus et les messages de synchronisation en temps réel en utilisant, peut saisir avec précision la synchronisation avec l'initialisation de l'enregistrement, ŕ long synchronisation, courte synchronisation et un bus données, et l'identification de descripteur correspondant, les tables de descripteur de commande pour les données transmises par l'hôte, ŕ la transmission et l'analyse des statistiques en temps réel affiche l'interface GUI. un message de bus de simulation de cadencement de transmission représenté sur la Fig.

Cette utilisation de conception CPU8245 différents systčmes d'accueil pour surveiller un grand nombre de tests analytiques et de vérification d'injection de défaut, le résultat de la vérification est compatible avec les caractéristiques de conception, remplacer complčtement des équipements coűteux, le personnel et l'analyse des temps et d'une solution efficace pour le bus systčme apparaît ARINC659 une variété de panne du bus.

3 Conclusion

Cet article est basé défaillance du systčme de bus ARINC659 dans le systčme de l'aviation dans le domaine souvent, le suivi, l'analyse des problčmes, un systčme d'analyse de positionnement et de bus rapide analyse l'état du bus pour une solution aux défaillances sur le terrain du systčme de bus ARINC659 problčme fourni, alors que l'analyseur il comprend un diagnostic de défaut, le traitement de l'information, la surveillance en temps réel, la capture de données et d'autres caractéristiques et l'injection de fautes, réduit la complexité du systčme, le systčme de bus pour ARINC659 aéronautique analyse efficace, en temps réel de l'état du bus pour fournir un moyen efficace.

références

Une spécification rinc bus de données 659 de fond de panier .Le compagnies aériennes Electronic Engineering Committee.Seattle: Blake Island, 1993.

Nouvelle forte, Tazawa, Huai Zhihua. La construction de la plate-forme de prototypage FPGA pour ARINC 659 et mise en uvre Génie informatique et conception, 2010,31 (12), 2726-2728.

Conception et mise en uvre de Wang Dina, Fan Xiao-ya, un Jianfeng .ARINC659 carte moniteur de bus Micro-électronique et informatique, 2010 (11): 168-172.

Tazawa, ning, Guo Liang, et bus de données .ARINC659 fond de panier et de la technologie clé Applications informatiques, 2013,33 (S2): 49-53,56.

avantages de l'adhésion AET de fin d'année!