AI se développe rapidement, la demande de puissance et ŕ plus grand nombre puce mémoire et plus, mais la loi de Moore ralentir ou męme pas faire la puce en utilisant la technologie de semi-conducteurs pour améliorer les performances de la puce et l'efficacité énergétique de plus en plus difficile. Ŕ ce stade, les deux derničres années dans le marché des puces est encore dominante géants de la technologie de puces ont développé puce AI, un nouveau type de puce et la technologie ont commencé ŕ émerger. Ainsi, eFPGA Cette technologie intégrée FPGA sera de savoir comment promouvoir le développement de la grippe aviaire? conception eFPGA comment 7nm affecter le développement de la grippe aviaire?

Le droit et le développement accéléré du ralentissement de AI Moore

AI permet le développement rapide de l'assistant vocal intelligente est presque devenu un téléphone mobile standard, mais aussi haut-parleurs intelligents expéditions augmenter année aprčs année. En męme temps, de plus en plus de téléphones mobiles utilisent la technologie AI pour optimiser l'effet de l'album photo et caméra sont classés. Mais ce ne sont que quelques-unes des techniques d'intelligence artificielle communes ŕ ce stade de l'application évolutive, nous algorithmes AI AI sont combinés avec plus d'industries et d'applications, de nouveaux algorithmes AI, quelle que soit la mémoire de comptage de la puce et donc la force ou mettre en avant des exigences plus élevées, toutes les sociétés de premier ordre AI dans la recherche de performances plus élevées, une faible consommation d'énergie, surface de la puce plus petite.

Revenant sur l'histoire de la performance de la puce, entre 1986 et 2003, la performance de la puce et la consommation d'énergie continue de diminuer aprčs 2003, en vertu des avancées de performance multi-core dans la conception de la puce et le processus de semi-conducteur est toujours dans la mise ŕ niveau, mais la loi de Moore il a clairement ralenti. Aprčs 2015, de plus en plus difficile de mettre ŕ jour la puce, la discussion sur la loi de Moore, de plus en plus d'échecs.

Les slows loi de Moore

Par conséquent, CPU, GPU, FPGA, amélioration de la performance ASIC et faible consommation d'énergie font face ŕ des défis croissants, en outre, ŕ partir de 7 nm nud 16nm, les coűts de fabrication de puces sont également considérablement augmenté. Pour une vitesse de calcul, le transfert de données, besoins en bande passante mémoire sont élevés puce AI, comment obtenir une meilleure performance par watt et ŕ moindre coűt?

Comment changer l'architecture AI eFPGA de?

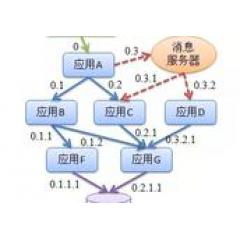

Pour puce AI, la conception de puces de plus en plus d'entreprises utilisent l'architecture multi-core hétérogčnes pour améliorer l'efficacité de la puce pour répondre aux besoins des algorithmes d'apprentissage en profondeur. En plus d'une architecture multi-core hétérogčne, l'architecture de noyau en béton sont constamment optimisés aussi pour AI, FPGA ne fait pas exception. Il est intéressant de noter, a été créé en 2004 et son sičge social aux États-Unis Achronix fournit une technologie FPGA embarqué. Le Achronix Speedcore IP peut ętre intégré dans un ASIC SoC et intégré FPGA (eFPGA), comme un co-processeur et des accélérateurs matériels peuvent ętre configurés pour supporter une variété de tâches, dont le bit de guidage (orienté bit) FPGA l'architecture, que l'architecture CPU (orientée mot) axée sur le terrain est plus efficace pour désinstaller SQL, le traitement d'E / S en ligne, le cryptage, l'accélération algorithme de recherche du moteur et de traitement multimédia des fonctions améliorées.

Selon Lei Feng réseau ŕ comprendre, Achronix est la seule entreprise ŕ offrir la technologie eFPGA a été intégrée dans la production de masse de la société ASIC, Speedcore IP nuds de processus applicable, y compris TSMC 16nm FF + et Intel 14nm FinFET, et a annoncé qu'il commencera la premičre moitié de 2019 fournir quatričme génération Speedcore eFPGA IP 7 nm adapté aux processus TSMC.

Achronix vice-président du marketing Steve Mensor

En plus de supporter la plupart des procédés de fabrication de pointe, de 7 nm eFPGA également optimisé l'architecture, ce qui est trčs critique pour le processeur de la machine d'apprentissage (MLP) a augmenté module d'unité logique de bibliothčque de ressources Speedcore ętre fournie. Steve Mensor vice-président du marketing chez Achronix exprimé: « module MLP est un moteur de calcul trčs flexible qui est étroitement couplé ŕ la mémoire, l'utilisation des propriétés spécifiques de l'intelligence artificielle et processus d'apprentissage de la machine, les performances de ces applications peut augmenter de 300%. tout en améliorant le rendement et le nombre d'opérations par cycle d'horloge, un MLP dans un cycle d'horloge pour effectuer un calcul de 16 x 16, 8 x 88 de calcul, le calcul est 126 × 6, 164 × 4 opérations ".

Les types de données peuvent ętre trčs précieux pour l'apprentissage de la machine, MLP est rapporté pour soutenir divers formats ŕ virgule flottante fixe et, y compris peu Bfloat16,16, demi-précision, bloc unité de virgule flottante 24 et, en fonction de l'application peut ętre sélectionnée qui est meilleure précision la précision et des performances équilibrées. Quant ŕ la question de savoir si l'accent sera mis sur les types de données pris en charge par le support, Steve leur a dit Feng Lei réseau eFPGA supporte tous les types de données, qui sont les avantages de la ligne programmable FPGA.

Bien que capable de supporter tous les types de données, mais l'accčs aux données de consommation d'énergie est plus que le problčme de la consommation d'énergie calculée tous les jetons AI doivent faire face. Ŕ cet égard, Steve dit: « MLP Chaque cycle comprend un fichier de registre (Fichier registre Cyclique), pour stocker des données ou du poids de réutilisation, sans passer par le LUT, d'améliorer les performances de traitement tout en réduisant la consommation d'énergie. »

En outre, on calcule pour l'application de l'apprentissage machine densité relativement élevée, si pas en mesure de répondre ŕ l'opportunité MLP, la table de Speedcore Gen4 (LUT) en tant que complément, peut ętre mis en oeuvre indépendamment FPGA de deux fois plus élevé multiplicateur.

Non seulement les performances d'apprentissage de la machine, Steve a dit: «Notre unité logique 7nm eFPGA, le câblage, l'architecture de routage, la mémoire est améliorée » Plus précisément, la table de consultation d'une amélioration globale, y compris les changements ŕ l'ALU taille double le nombre doublé de registres chaque LUT, un certain nombre de fonctions de support et sept huit fonctions, et fournit un registre ŕ décalage dédié ŕ la liaison ŕ haute vitesse, ce qui réduit la zone et la consommation d'énergie et d'améliorer le rendement. En outre, l'architecture de routage obtenu ŕ partir d'une structure séparée, bus dédié amélioré de routage, la structure de routage dédiée multiplexeurs de bus, peut créer effectivement distribué, la configuration de l'exécution réseau de commutation, et premičre fois ŕ appliquer ŕ l'optimisation du réseau d'interconnexion FPGA de l'industrie.

conception de la puce et de l'architecture optimisée dans le processus de bienfait 7 nm, Speedcore Gen4 d'augmenter les performances de 60%, les performances d'apprentissage de la machine une augmentation de 300 pour cent et la consommation d'énergie de 50%, une réduction de 65% de la superficie de la puce.

mise ŕ niveau Speedcore Gen4 FPGA

Tout en poussant IP et 7 nm eFPGA application indépendante FPGA ne AI

AI que de changer la structure des aspects eFPGA, Steve 7nm représente noeud de processus TSMC Speedcore Gen4 sera dans la production de volume de la premičre moitié de 2019, et fournira Speedcore Gen4 eFPGA pour le nud de processus de 16nm et 12nm TSMC dans la seconde moitié de 2019 IP.

Lei Feng réseau noté, non seulement dans la fourniture de noeud Achronix IP eFPGA 7 nm, fournit également FPGA die peut ętre emballé avec le SoC, et introduira également un des dispositifs indépendants de FPGA. Quant ŕ savoir pourquoi la fourniture Achronix IP pour lancer un FPGA indépendant dans le noeud 7 nm, Steve a dit: « Il est plus d'une considération en fonction des besoins des utilisateurs dans l'application de l'intelligence artificielle, d'accélérer le centre de données, 5G, a un pilote automatique différent. besoins assez de FPGA plus indépendants pour leur permettre d'application plus rapide dans le centre de données, pour obtenir l'accélération, mais aussi pour mieux répondre aux besoins du montant de la puce 7nm FPGA petites entreprises. ceux qui sont plus sensibles aux coűts et surface de la puce, ou si vous voulez conception AI des sociétés de premier ordre de performance plus élevé, vous pouvez sélectionner IP. bien sűr, les entreprises SoC peut choisir la technologie d'emballage droite, nous allons mourir avec eux l'encapsulation SoC, obtenir un meilleur rendement ".

Luo Wei, directeur général de l'Asie-Pacifique Achronix lumineux

Bien sűr, le matériel est fondamental, le logiciel jouera également un rôle de plus en plus important dans l'IA, de nombreuses sociétés de conception de puces ont commencé ŕ coopérer davantage avec la société de logiciels dans l'čre AI, mais lors de la conférence de presse, en plus des outils de conception ACE Achronix et aucun autre logiciel pour l'IA. Steve a dit ceci: « Nous, comme en plein développement, mais l'échelle est pas grande entreprise assez, actuellement, nous fournissons principalement un puces différentes stables et rentables au niveau du matériel, nous le ferons Libiary plus haut niveau, le logiciel est plus en collaboration avec des partenaires. "

Qui a besoin moindre coűt eFPGA 7nm?

Jusqu'ŕ présent, nous avons appris, en termes de conception architecturale ou du côté de la demande, eFPGA sont optimisées, mais il y a une question trčs critique est de traiter 7 nm de 16nm mis sur la performance, la consommation d'énergie face ŕ l'amélioration des coűts semble assez attractif . Alors que Steve, entreprise de conception puce eFPGA 7nm prix d'achat IP et 16nm eFPGA IP par rapport au prix n'a pas augmenté, mais les coűts de production ont fortement augmenté, ou faire beaucoup de sociétés de conception puce prohibitif.

Steve représente, 7 nm eFPGA principal marché, y compris les exigences de prix et de performance de calcul de l'accélération du centre de données, le calcul d'un bord de la faible consommation d'énergie de l'informatique, de faible consommation d'énergie et faible coűt de la mémoire, des performances élevées et une faible consommation d'énergie requise il infrastructure programmabilité 5G, l'accélération réseau / carte ŕ puce, pilote automatique.

marché eFPGA 7nm

Cependant, certaines applications sont des marchés potentiels, d'autres sont un facteur clé de Achronix lancé eFPGA 7 nm. Steve a dit: « Ŕ l'heure actuelle, nos revenus sont les deux applications l'infrastructure 5G et les cartes ŕ puce les plus importantes (SmartIC), 5G haute performance et les exigences de faible puissance de la puce, donc beaucoup d'entreprises utilisent maintenant FPGA précédemment transférés ŕ ASIC, mais il a besoin d'une certaine flexibilité pour répondre aux changements dans l'accord. carte ŕ puce est ensuite traitée des données avant la transmission de données, nous savons que la quantité de données et la complexité des données augmentent, de sorte que ces deux scénarios pour 7nm eFGPA a une trčs grands centres de données ŕ la demande, et automatisée de conduite, effacer tous les besoins de stockage, comme les bords calculer la plus appropriée scčne que vous devez voir le développement du marché ".

Il est également ŕ noter que, afin d'accélérer l'application du centre de données de la charge de travail d'apprentissage de la machine et de l'automobile, la combinaison eFPGA Achronix avec la mémoire de GDDR6 Micron, dans la quatričme génération amélioration eFPGA 8 GDDR6 de l'interface mémoire ŕ travers laquelle les espčces de la solution mixte, la profondeur du réseau de neurones peut traiter de grands ensembles de données comprend le stockage, et le paramčtre re-pondération activation de mémoire; nécessité de remettre en question le magasin de matériel sous-jacent, de traiter et d'autres données en mouvement rapide entre le processeur et la mémoire.

Lei Feng réseau Résumé

algorithmes AI sont constamment itération et le développement, et donc plus polyvalent de la CPU, GPU, bien que capable de compléter l'algorithme correspondant, mais de plus en plus inefficace et plus coűteux, qui a favorisé les innovations d'architecture de puce. Nous voyons de plus en puce multicur plus hétérogčne utilise AI pour améliorer la performance et l'efficacité grâce ŕ différents portefeuille de base pour mieux répondre aux besoins de l'IA.

De l'amélioration Achronix eFPGA de nous voyons aussi que dans l'unité logique, le routage, l'architecture de routage ont été améliorés, et une augmentation du MLP, de réduire le traitement des données de consommation d'énergie, également équipé d'une mémoire sur puce, et afin de résoudre l'étude approfondie le problčme inhérent, le premier ŕ soutenir GDDR6 dans le FPGA.

puce AI AI est de promouvoir l'application de l'intelligence artificielle pour aller de l'avant dans cette interaction.