On peut prévoir, avec le déploiement des réseaux 5G dans le monde aurait une vague massive d'expansion, et nécessite beaucoup de redresseur de télécommunications de haute qualité pour fournir la puissance nécessaire. Afin de satisfaire ŕ améliorer l'efficacité, réduire les coűts d'exploitation et de la baisse de la demande facture du coűt des matériaux, une solution large bande interdite pour les personnes regain d'intéręt. De męme, les gens essaient constamment de mettre ŕ niveau la puissance du serveur, donc l'efficacité énergétique a continué ŕ améliorer, alors que la perte de chaleur au minimum. Maintenant, la puissance de l'économie numérique, les grandes données, les réseaux et l'intelligence artificielle de données ultra-grande échelle racks de serveurs centrale en utilisant plus de 30 kW et le fonctionnement du systčme de gestion de refroidissement hautement sophistiqué.

Un réseau d'antennes ayant une plus grande (jusqu'ŕ 64 d'émission / réception 64), permettra d'améliorer le débit de données et des services en pli 100-1000 dispositif de réseau 5G constituant les billions de choses, il semble que nécessitent plus de puissance. Pour réduire la puissance nécessaire pour chaque station de base, il y a eu de nombreuses améliorations techniques, mais il peut exiger plusieurs stations de base. Afin de fournir la méthode de gestion avancée de l'alimentation, de l'état de veille ŕ la pleine charge, la puissance de ces stations de base doit satisfaire aux exigences en matičre d'efficacité de plus en plus strictes.

FET SiC nouveau produit peut atteindre des objectifs d'efficacité inatteignables, et nous allons étudier la topologie principale et la fonctionnalité de l'appareil dans cet article. Nous allons discuter de la situation dans ce domaine, nous pouvons apprendre, dans ce domaine, le silicium super-jonction, FET SiC et de nitrure de gallium (GaN) FET participeront ŕ la compétition.

quelques notions de base

L'alimentation de courant est un segment de correction de facteur de puissance (PFC) qui sera proche de facteur de puissance unité alternatif en courant continu, la tension de sortie de 400V, est suivi d'un convertisseur de courant continu, qui convertit le 48V ou 400V convertis en 12 V, pour une utilisation dans le systčme. Ensuite, les autres convertisseurs de point de charge du processeur et ŕ l'alimentation du magasin.

Si vous vérifiez la puissance centre de données l'utilisation du serveur, il est clair que la majeure partie de sa vie est consacrée ŕ la charge légčre. En conséquence, la section PFC et DC - DC segments doivent avoir un rendement élevé dans toutes les conditions de charge, mais aussi pour répondre ŕ l'opération de charge maximale des contraintes thermiques. Pour le calcul de l'alimentation 80 Plus bien standard connu cela peut apparaître comme représenté sur la figure. serveur de titane doit répondre aux critčres, mais aussi de maintenir un rendement élevé, męme sous une charge de 10%. La figure 2 montre le programme ouvert informatique (Open Compute Project) spécifications typiques, les exigences de la spécification que l'alimentation standard de qualité de titane 3.3kW.

Figure 1: montre un des objectifs d'efficacité de puissance calculée norme 80+

Figure 2: serveur informatique 3.3kW spécifications de puissance du plan ouvert

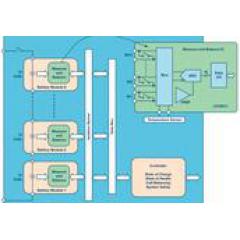

La figure 3 montre une architecture de puissance typique, comprenant un pont redresseur d'entrée, avec un simple deux diodes convertisseur élévateur intercalées FET 650V (PFC) et de la barričre de jonction SiC Schottky (le JBS) et la LLC pont complet étape DC convertisseur. Non représenté sur la figure d'entrée filtre EMI. Une fréquence typique de commutation de l'étage PFC est utilisé 65-150kHz. Ici, la densité de puissance nécessaire ŕ un compromis, afin d'atteindre une plus grande efficacité ŕ des fréquences plus basses, car plus bas plutôt que 30kHz 150kHz commutateur, un inducteur sera plus petite. Il en résulte la nécessité de silicium utilisé avec MOSFET de jonction super diode JBS SiC pour maintenir un rendement élevé tout en étant commutation dur ŕ 65-150kHz. commutateur MOSFET de jonction super trčs avancé rapidement, et de faciliter l'ouverture de la diode Schottky SiC pour minimiser la perte du MOSFET.

Figure 3: configuration d'alimentation commune. Aprčs le pont redresseur d'entrée, sont le niveau de qualité et entrelacée PFC LLC pont complet

Dans le circuit de l'étage de LLC, habituellement utilisé MOSFET 650V. Le circuit maintient une opération de commutation de tension (ZVS) zéro et en réduisant le courant de fermeture, et donc beaucoup moins de pertes, et de permettre un fonctionnement ŕ des fréquences plus élevées 100-500kHz de sorte que le transformateur plus petit. Dans la partie secondaire, une faible résistance du transistor MOSFET silicium 80-150V pour redresser la fréquence secondaire de tension alternative, afin de fournir une tension de sortie ŕ courant continu stable. Lorsqu'il est utilisé avec FET 650V, de sorte que ZVS est perdue dans certaines conditions d'exploitation, la récupération de la diode parasite ne causera aucun dommage.

Dispositif semi-conducteur

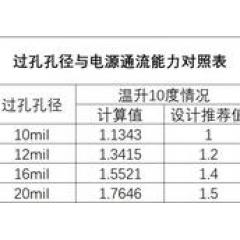

transistors Look aspect, l'étage PFC et le côté haute pression du convertisseur de courant continu, généralement périphérique 650V-classe. Le tableau 1 résume la derničre technologie de dispositif en silicium, les dispositifs de GaN et des dispositifs de SiC et les propriétés connexes. Sur la résistance par unité de surface (le CSRD) impact en termes de la taille de la puce, jusqu'ŕ présent, FET SiC (JFET SiC du CSRD) est le meilleur choix. Produit par rapport ŕ la Superjunction de silicium Sinon, tous les appareils ont une excellente grande performance de récupération diode parasite bandgap. Cependant, seul dispositif de SiC et du silicium capable de dispositifs de traitement d'avalanche énergie. La tension de seuil du dispositif ŕ mode d'enrichissement de GaN (Vth) est faible, couplé avec sa tension de grille et une plage de vitesse plus étroite, ce qui rend difficile ŕ conduire.

Tableau 1: 650V transistor de comparaison Basic Technique Option

Le tableau 2 présente une comparaison de certains de l'industrie du paquet TO247 populaires produits équivalents. Super-silicium jonction (Si SJ) et le dispositif peuvent ętre entraînés par les produits UnitedSiC 0 ŕ 10V entraînement. option de SiC MOS nécessite des tensions différentes (par exemple -4V ŕ 18V). dispositifs de SiC ayant chacun une faible capacité d'entrée (charge de grille), et de réduire considérablement la diode de charge de récupération (Qrr). la perte de conduction diode parasite superjonction silicium et SiC FET est plus faible que le MOSFET SiC.

Tableau 2: Paramčtre Type de paquet TO247 transistor comparaison similaire

Le tableau 3 montre une comparaison entre l'espace de carte dispositif similaire DFN8 × 8. silicium super-jonction, les dispositifs FET de SiC et GaN peut ętre entraîné par un pilote standard de grille de silicium. Le produit FET UnitedSiC a une trčs faible résistance. Caractérisation des trois derničres lignes de la comparaison est de préférence utilisé avec différents 150 RDS (ON) de l'appareil. Une large solution de bande interdite fournit une meilleure caractérisation, en particulier pour Rds * Coss (tr) et Rds * Qrr.

Tableau 3: DFN8 de type paquet de 8 paramčtres de transistors d'attaque de silicium compatible Comparaison

La figure 4 montre le FET SiC, GaN FET et l'architecture du FET de superjonction de silicium utilisée configuration en coupe transversale. GaN HEMT est un dispositif latéral, et d'autres types de dispositifs sont des dispositifs verticaux. Dispositif de circulation de courant vertical de telle sorte qu'une tension plus élevée peut ętre plus compacte parce que le terminal source et le stade terminal de vidange situé sur le côté opposé de la tranche plutôt que sur la surface supérieure. Dans le GaN HEMT, un canal de conduction d'électrons ŕ deux dimensions est limité ŕ gaz (2 DEG), et les dispositifs ŕ canal de surface SiC en utilisant un court, mais la plupart de l'exécution en cours. canal JFET SiC ayant un grand volume, avec sa caractéristique verticale, sa résistance par unité de surface (la RDSA) minimum, la taille de la puce est minime. Ensuite, un transistor MOSFET silicium en cascade basse pression (augmentation de 10% de la résistance), pour former un FET SiC.

Figure 4: Architecture de dispositif semi-conducteur de l'art dans le centre de données et l'alimentation électrique de télécommunications utilisé dans la compétition 650V

Avec des dispositifs améliorés, la limite finale est déterminée par la vitesse de commutation du courant de charge du dispositif de la sortie de capacité de charge Coss. Pour une donnée sur la résistance, de faibles valeurs Coss (tr) peut fournir la vitesse de balayage la plus rapide, et pour obtenir un temps de retard minimum de 400V. Comme il ressort du tableau 3, la performance FET SiC est trčs bon ŕ cet égard, il est un bon choix et une conversion de puissance ŕ haute fréquence.

Qrr sur, par rapport ŕ dispositif super-jonction ŕ base de silicium, les performances d'un large choix de bande interdite sont grandement améliorées. Ainsi, tant que le circuit tel qu'il est utilisé dans le mode courant continu (CCM) PFC dur interrupteur bipolaire totem est ouvert, pour sélectionner ces composants. Si ces circuits en utilisant les diodes parasites conducteurs dans l'état de roue libre, ŕ l'état chute de tension de la perte de conduction de diode parasite résultera. Ainsi, la synchronisation est généralement utilisé conducteur, le canal FET est ouvert pour réduire ces pertes. Détecter un courant inverse de l'ouverture il y a généralement un décalage entre le canal FET, ŕ haute fréquence, cette fois, est une partie importante du cycle de commutation. Par exemple, si la fréquence de commutation est de 100 kHz (période de 10us), le temps mort est 100ns, la diode conductrice dans l'intervalle, est sans importance. Mais ŕ l'intérieur de 1MHz (1000ns période) du cycle de commutation, il devient alors 10%. En conséquence, la diode parasite conduisant une chute ŕ basse pression et ŕ faible VSD Qrr sont des fonctionnalités utiles, les deux FET SiC est trčs faible.

De plus, l'option la plus efficace peut éviter circuit dur ouvert, car bien que de larges dispositifs de bande interdite désactivent la perte est négligeable, mais le tour sur les pertes ne sont pas négligeables. Disponible par la charge de grille FET est faible, faible résistance et désactiver la perte peut ętre 5-10 fois la fréquence circuit de commutation douce.

En termes de robustesse dispositif, toutes les options SiC a une excellente capacité d'avalanche, ce qui améliore la fiabilité du systčme de conversion. Malgré sa petite taille de la puce, mais généralement il peut dépasser la capacité du TEC super jonction, en particulier aux niveaux actuels élevés. dispositifs GaN ne peuvent pas gérer l'avalanche, ainsi conçu pour avoir une tension de claquage élevée, afin d'éviter cet espace de travail. La figure 5 montre le 40Mohm de UnitedSiC, pointe FET SiC 650V 80A avalanche plage de tolérance de courant (bleu), ce qui est bien au-delŕ des besoins pratiques. On a observé dépasse la tension de claquage de 800 V (vert).

Figure 5: UF3C065040K4S (40Mohm, dispositif FET SiC 650V) non amortie forme d'onde de test inductif. Bien que SiC JFET petite taille, mais le dispositif peut résister ŕ plus de courant 80A sans avalanche échec

Considérations Gate Drive

Utilisation du FET SiC est essentiel que le simplifié, le transistor MOSFET basse tension ayant une tension de seuil VTH 5 V et +/- 25 V au maximum tension grille-source VGS d'étoiles (MAX). Il peut ętre le męme que le super silicium MOSFET de jonction conduit ŕ 0 ŕ 10V (ou 12V). La figure 6 est une comparaison avec la tension de commande de grille recommandée correspondante de la grille du diverses techniques Note maximale absolue. MOSFET SiC conducteur de grille généralement négative et positive, et l'excursion de tension de grille requise totale de 20 ŕ 25V. La tension de grille est généralement trčs proche des cotes maximales absolues, ce qui nécessite une attention particuličre aux pointes de porte. Grand swing porte ŕ des fréquences plus élevées peuvent ajouter des pertes de charge de grille considérables. De plus, pour gérer la tension de seuil problčme d'hystérésis de VTH, il faut suivre attentivement les recommandations du fabricant pour déterminer le niveau de tension de commande de grille. FET SiC est trčs flexible ŕ cet égard, non seulement ne nécessite pas le niveau de tension de grille de façon soigneusement contrôlée et peut ętre entraîné ŕ la tension de grille compatible avec le MOSFET SiC.

Figure 6: graphique comparant les différents types de silicium et des dispositifs de SiC et de la tension de grille de l'unité de grille calibre maximum recommandé. SiC FET polyvalence unique

Mode d'amélioration des dispositifs de GaN ont généralement une tension de seuil Vth basse, l'entraînement et la tension de grille dans une plage étroite, laquelle plage est généralement trčs proche de la limite absolue de la tension grille-source VGS maximales. Cela nécessite un pilote spécial et la mise en page soigneusement pour éviter d'endommager l'interrupteur. option cascode pour éviter certaines de ces difficultés. Lower portail battant de tension dispositif ŕ enrichissement contribuera ŕ réduire les pertes de grille ŕ des fréquences plus élevées.

Dans tous les cas, lorsque le dispositif est utilisé ŕ une vitesse plus élevée, un haut dv / dt des dispositifs fermés de maintien devient plus difficile. Les pointes de tension de grille inductance de boucle de puissance en boucle de la direction et le conducteur de grille aussi bien. Avec l'aide de broches de paquet niveau de la source Kelvin ont un rôle important, mais nous présenterons d'autres options dans le présent document plus tard.

topologie du circuit Niveau -PFC

La figure 7 montre un circuit PFC totem pôle (TPPFC), et l'utilisation du type FET SiC UJC06505K UnitedSiC carte de démonstration 1.5KW ŕ l'efficacité mesurée 100kHz. Ce circuit élimine toutes les pertes de conduction de la diode d'entrée des diodes de pont de diodes et SiC PFC. Dans ce cas, le convertisseur fonctionne en mode mode de courant (CCM) en continu, et le dispositif est un disque interrupteur.

Figure 7: circuit totem pôle de base PFC, et l'efficacité des données par rapport ŕ une norme de titane, en utilisant le type de données FET UJC06505K SiC mesurée ŕ la carte de démonstration UnitedSiC

La figure 8 montre une coupe TPPFC ętre utilisé avec les inducteurs couplés ŕ la conception. Le circuit peut ętre utilisé dans un mode de courant continu, peut également ętre exploité ŕ une fréquence plus élevée dans le mode de conduction critique, telles que la mise en marche des pertes peut ętre éliminé. FET SiC peut ętre mis en oeuvre en utilisant une densité de puissance trčs élevée sans sacrifier l'efficacité, bien au courant d'entraînement supérieur et lorsque la détection de passage ŕ zéro actuel doit ętre sous le contrôle de la complexité magnétique et une plus grande de la conception.

Figure 8: totem pôle entrelacée PFC, en utilisant deux interrupteurs et un interrupteur en demi-pont de la fréquence de ligne rapide. Le procédé permet le fonctionnement de l'inducteur couplé en utilisant le mode de conduction critique, ce qui peut augmenter de façon significative la fréquence

Le tableau 4 montre la figure l'échelonnement des entrelacées topologie de totem pôle PFC. 8 et Fig. 1 Comparaison de la subdivision de perte PFC. Dans les deux cas, nous supposons un convertisseur de 3KW fonctionne ŕ une fréquence de 100 kHz chaque commutateur. Des moyens d'entrelacement que la fréquence d'ondulation de l'inductance de 200 kHz. totem pôle PFC réduire 25.7W (par rapport ŕ 51.4A), permettant ainsi une cible de titane norme efficacité nette. Ceci est réalisé en éliminant le pont redresseur perte 24.3W. totem pole PFC utilisé dans cet exemple a besoin de plus de quatre FET et un pilote de porte.

Tableau 4: la perte et de la complexité intercalés PFC et le circuit PFC ŕ l'aide du totem UJC06505K 100kHz pour atteindre en mode CCM 3KW Comparaison

Une autre méthode est nécessaire pour détecter traversée de courant au moyen de commutateurs auxiliaires supplémentaires, afin d'obtenir une conversion de tension nulle ŕ l'air libre. Auxiliaire Resonant Commuté Pole en utilisant cette technique de résonance (l'ARCP) ou analogue peut ętre ouvert et fermé pour éliminer les pertes, de maničre ŕ obtenir des résultats similaires ou mieux. Cependant, seulement lorsque la puissance est beaucoup plus élevé que 5KW, un avantage de coűt de la technologie plus avancée.

topologie circuit - DC - DC niveau

Etant donné que la tension de sortie est fixée, et donc convertisseur LLC pont complet de. La figure 1 fournit une excellente densité d'efficacité et de puissance, et est devenu les principales applications industrielles de niveaux de puissance élevés. Comme la puissance est réduite, les modes de réalisation peuvent utiliser un LLC en demi-pont. gamme de fréquences commune de 100 - 500, en tenant compte du niveau de 12V haut rendement courant, ce qui réduit la perte d'emplois critiques au transformateur secondaire et le MOSFET côté MOSFET secondaire.

Pour la haute pression du FET, la tension drain-source VDS ŕ partir de son état fermé ŕ une diode ŕ conduction est nécessaire pour faire passer le condensateur de sortie est chargé, et pour charge rapidement, COSS (TR) doit ętre faible. Cependant, l'utilisateur doit réduire au minimum le temps mort avant la conductrice de synchronisation, une diode parasite pour réduire les pertes de conduction dans la porte du FET. Une faible résistance ŕ l'état ON peut réduire l'énergie de perte de conduction fermée super-jonction et la plupart du faible EOFF large de commutation bandgap les pertes de commutation facilitent réduit au minimum.

Si la perte ZVS dans des conditions de faible charge, la diode de récupération de disque peut se produire. Pour large commutation de bande interdite (par exemple FET SiC), bien que cela ne pose aucun risque, mais endommager le MOSFET de jonction super de silicium. Pour minimiser cette possibilité, utilisée version du TEC de jonction récupération ultra-rapide, mais vous n'avez pas besoin de prendre de telles précautions FET SiC.

Perspectives récentes

Bien que la super-jonction amélioration FET de silicium se poursuit, mais les prochaines années pour améliorer le niveau des dispositifs SiC et GaN sera possible d'obtenir beaucoup plus que les dispositifs de silicium peuvent atteindre le niveau. En plus d'améliorer la résistance CSRD par unité de surface (30-50% tous les 2-3 ans), la technologie de l'emballage devrait il y aura de nombreuses améliorations. Le principal défi ŕ relever est une faible inductance et une petite surface de montage des options sur la façon de la chaleur se dissiper plus efficacement.

Une façon possible consiste ŕ passer ŕ un demi-pont conçu pour l'élément de fixation de surface directe conçu pour ętre utilisé comme un élément de demi-pont ou des éléments noyés dans la carte de circuit. Ceci permettra de simplifier la mise en page de carte de circuit, et permet une grille inférieure et une boucle de puissance inductif.

Dispositif de puissance ŕ entraînement intégré Un autre nouvel itinéraire est ajouté sous forme d'un seul disque ou comme éléments de commutation en demi-pont. Comme la plupart des appareils périphériques SiC et GaN requičrent un niveau de tension du circuit d'entraînement unique, un tel complexe peut ętre co-emballés ou intégrés dans le produit absorbant, ce qui rend plus facile pour l'utilisateur. En outre, chaque appareil peut alors mieux jouer son plein potentiel. Sans aucun doute, cela réduira le coűt du systčme et la consommation d'énergie, et promouvoir l'utilisation d'un large dispositifs de bande interdite.

Le long de ces lignes, avant que les présents articles sont décrits dans les conducteurs de grille de demi-pont SIP série avec un demi-pont intégré, l'utilisation de la 35mohm d'entraînement, 1200V FET SiC. De nombreux fournisseurs offrent des options de montage en surface, et cette tendance est susceptible d'accélérer.

650V large bande interdite coűt de commutation est maintenant en déclin rapide. Est attendue dans les deux prochaines années, UnitedSiC du FET 650V sera proche du prix des dispositifs de silicium. Avec la facilité d'utilisation, cette tendance devrait accélérer rapidement le déploiement de larges dispositifs de bande interdite dans les applications de serveur et d'alimentation des télécommunications.