Yangxue Bo, LI Lei 1, 2 Chen Rio

(1. Institut des sciences et de la technologie électronique, Université de science et technologie de la Chine, Chengdu 6117302. École de génie électronique, Chengdu Université de technologie de l'information, Chengdu 610000)

Avec le développement rapide de l'équipement vidéo, les applications liées ŕ la vidéo numérique ont également développé rapidement, tels que les équipements de surveillance, tachygraphe et les téléphones mobiles et autres produits électroniques. Aujourd'hui, les algorithmes d'amélioration de l'image vidéo numérique aprčs l'autre, en raison de la complexité de l'algorithme est relativement élevé, il est difficile de répondre aux exigences de base de temps réel. Sur la base des pixels d'image traitées sont discutés modčle Retinex dimension étirée et la technologie clé modules de touche configurable de la simulation et de la pratique, enfin, la mise en uvre (Vertex-5) par le FPGA, l'horloge systčme 125 MHz, répondre ŕ la 30 f / s image (2000 x 2048) pixels.

Retinex; amélioration vidéo; FPGA; traitement en temps réel

TP317.4

Code de document: A

10,16157 / j.issn.0258-7998.2016.11.008

format de citation chinois: Yangxue Bo, Li Lei, l'extension Chen. Les algorithmes clés d'amélioration de la vidéo couleur sur la technologie FPGA Technologie électronique, 2016,42 (11): 37-39,43.

Anglais format de citation: Yang Xuebo, Li Lei, Chen Guangtuo, et al. Technologie clé de l'algorithme d'amélioration de la vidéo couleur et la mise en uvre FPGA .Application Technique électronique, 2016,42 (11): 37-39,43.

0 introduction

Technologie d'amélioration vidéo large éventail d'applications, telles que l'électronique médicale, le contrôle industriel, l'électronique grand public et l'exploration spatiale profonde. la théorie Retinex a été proposé par Edwin Land en 1971. modčle Retinex basé sur l'utilisation d'une seule échelle plus large algorithme Retinex (échelle unique Retinex, SSR), un algorithme Retinex multi-échelle (Multi échelle Retinex, MSR), multi échelle algorithme Retinex avec correction des couleurs (Multi échelle Retinex avec restauration des couleurs, MSRCR), un algorithme basé sur un modčle a priori comme points de débat algorithme Retinex basé sur le cadre, mais la complexité de cet algorithme est trop élevé peut consommer des ressources matérielles excessives, vous ne pouvez pas obtenir une bonne application dans la pratique. L'échelle mono ou multi-échelles de l'algorithme Retinex que l'amélioration significative de l'image reconstruite de la configuration matérielle primaire d'un algorithme Retinex multi-échelle est une échelle de circuit matériel unique algorithme Retinex. Ce but de papier ŕ des améliorations technologiques clés du matériel algorithme vidéo d'étude, afin de prendre une seule échelle algorithme Retinex, cependant, pour un tel processeur algorithme ne peut pas répondre aux exigences de son traitement vidéo en temps réel, il utilise 125 MHz fréquence FPGA, rencontre 30 f / s de pixels d'image (2000 x 2048).

Cet article traite de l'algorithme ŕ clé de Retinex basée sur l'échelle de pixel d'image peut ętre étirée et configuré configurable. architecture matérielle proposée peut adapter ŕ différents pixels pour la vidéo. Pour réaliser la conception et la simulation des modules clés, la conception FPGA pour atteindre l'ensemble du modčle par Vertex-5, évaluer enfin l'algorithme d'effet de traitement.

1 modčle Retinex algorithmes d'amélioration vidéo basé

La figure 1 est un organigramme d'un algorithme amélioration vidéo Retinex. image de trame vidéo de l'image de trame grise RVB sont converties dans HSV V, l'image trame chroma S, la trame d'image de saturation H. image de trame d'éclairement estimée, obtenue aprčs l'image composante de lumičre appropriée étirage et un compteur composant V2 V3. Aprčs le processus d'étirage, et aprčs le procédé de synthčse d'images est le O d'une image traitée.

1.1 tour RVB HSV

Étant donné que l'espace couleur RVB de l'image de traitement produisent directement la distorsion couleur, la conversion de l'espace colorimétrique est nécessaire.

1.2 image d'illumination d'extraction et de l'image inverse

image de trame d'origine I (x, y) peut ętre décomposé en deux parties . Une partie de l'image de trame lumineuse L (x, y), ce qui reflčte une autre partie de l'image de trame R (x, y), la formule (1) représentée sur la figure.

Ici filtre d'estimation d'éclairement Gaussienne, la composante ŕ haute fréquence (détail partie d'image et une partie de bruit) a été séparé par filtration.

1.3 Procédé de traitement de trame et le composant de traitement de composante de lumičre de réflexion

élément de réflexion peut ętre étirée non linéaire par une fonction sigmoďde. Dans ce puits supprimer le bruit tout en amplifiant le composant de détail utile.

1,4 ŕ HSV image RGB ŕ l'image

espace de couleur RVB est une couleur composée de rouge, vert et bleu pour l'affichage, l'image est convertie en RVB HSV.

2 vidéo architecture logique matérielle activateur

amélioration vidéo Adaptive l'architecture VLSI représenté sur la. figure 2,. La figure 2 est une partie de trame de mise en uvre de FPGA, la partie extérieure du cadre pour réaliser la conversion par le MATLAB. Le systčme de registres de configuration internes configurés par le décodeur module, la tâche principale est de configurer les pixels de l'image. tampon SRAM SRAM_interface est relié ŕ un flux de données d'image externe, l'allocation d'espace de mémoire pour la mémoire SRAM interne ŕ deux opérations de ping-pong des données vidéo. Filtre utilise une modification du filtre ŕ deux dimensions. Ce filtre peut ętre adapté ŕ différents pixels processus de filtrage d'image ŕ grande vitesse. Estimée par le filtre et en raison de la complexité de l'image de l'éclairage et de la soustraction du nombre est relativement élevé, de sorte que la luminosité élevée et de la distorsion de pixels, le papier de séparation de haute précision, pour obtenir une image réfléchie. Multiplicateur image améliorée en passant ŕ travers les deux fonctions processus d'étirement, restaurer l'image RVB via HVSRGB.

Le module de filtre amélioré aprčs 2,1

Sur la base du document peut ętre configuré pour gérer présente un filtre ŕ deux dimensions ayant une taille de pixel et de bonnes caractéristiques de synchronisation. Architecture illustré ŕ la figure 3. Papier filtre divisé en trois parties, la premičre partie de l'action est de fusionner deux données de 8 bits en données de 16 bits, et écrit séquentiellement dans différentes FIFO. La deuxičme partie est configurable FIFO, la profondeur FIFO configuré pour configurer un registre interne, la fenętre de filtre pour des données d'écriture dans des lignes différentes. La troisičme partie est un filtre ŕ fenętre, pour convertir 16 bits de données de 8 bits est écrit ŕ deux fenętre de filtre de pixel, le cycle suivant de ces deux pixels décalé en arričre ŕ deux pixels. Obtenue par les coefficients de filtre pour chaque nouveau cycle des pixels traités. Cette configuration permet non seulement des ressources, et peut ętre configuré pour traiter le nombre de pixels d'image vidéo, la fréquence d'horloge de traitement est la moitié de la fréquence d'horloge du systčme, pour mieux répondre aux besoins de synchronisation.

2.2 multiplicateur ŕ grande vitesse

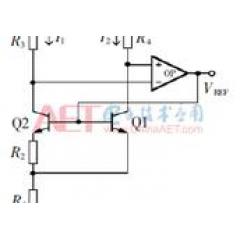

La conception utilise un certain multiplicateur , puisque les raisons de synchronisation multiplicateur ŕ grande vitesse décrit ici,. La figure 4 est un schéma de principe d'un multiplicateur de matériel, le multiplicateur comprenant un algorithme stand-4 et l'arbre Wallace composé par le CSA et super sommateur avance.

Et la partie de base de génération 4 algorithme de stand est, prčs de la moitié de la partie réduite et, par la CSA ŕ accumuler des unités d'arbre de Wallace, et les deux parties obtenues par l'additionneur préanalyse produit finalement obtenu.

2.3 diviseur

Un papier de séparation, de haute précision, étant donné que l'opération de réduire l'erreur générée par le circuit de matériel de séparation ŕ grande vitesse représentée sur la Fig. 5, un multiplicateur et tables consultation, table de consultation stockant l'inverse du diviseur.

2.4 étirage et réglage de l'image

image de trame de lumičre pour réaliser la correction de gamma, en utilisant la méthode de consultation de table décrit ici.

Image de réflexion ne opération d'étirage employée pour mettre en oeuvre l'architecture représentée sur la Fig. 6, l'configurable de traction ici, le présent procédé peut ętre mis en uvre en modifiant le degré de changement qui est étiré registre de Con. Modifier les effets de traitement d'image. Et Fun circuit de combinaison Fun1 utilisé pour implémenter la fonction.

3 simulation du module de base et les résultats expérimentaux

Etant donné que la capacité de modesim simulateur VCS pour la simulation de chaque module, tel qu'il est utilisé ici, le filtre de la mémoire du systčme d'exploitation Linux Debian 8 âme 16 du fil 48 G, la version de la plate-forme de simulation VCS, 2013, pour donner les résultats indiqués sur la figure 7, la figure 8..

Dans cet article Vertex_5_FXT (FX70 / 100T) _FF1136 plate-forme matérielle de la puce FPGA pour construire une partie essentielle d'un schéma fonctionnel interne de l'autre partie est réalisée par AMD 44 G mémoire noyau Matlab 2014b. La figure 9, la figure 10 est le résultat du traitement des différentes images.

4 algorithme d'évaluation

Entropy est un concept important de la théorie de l'information ŕ l'intérieur, représente la quantité d'informations dans l'image reflčte également combien le contenu de l'image . La formule (11) est une expression de l'entropie.

Avant et aprčs la mise en valeur d'image de l'entropie dans le tableau 1 tel que représenté sur la figure.

5 Conclusion

Cet article analyse l'algorithme d'amélioration de l'image vidéo Retinex basée sur des architectures différentes, a priori algorithme Retinex en raison de la plus grande complexité de l'algorithme, nous avons sélectionné une seule échelle la technologie clé de l'algorithme Retinex, aprčs algorithme de reconstruction seule échelle est l'algorithme Retinex multi-échelle, sur la base des pixels d'image sont agencés et une architecture proposée de traction peuvent ętre configurées ŕ l'échelle, et chaque module mis en oeuvre et la mise en uvre simulées FPGA Enfin, l'effet du traitement et l'évaluation d'image.

références

Wang Wen, Li Bo, Zeng Jin, et al.A rapide algorithme de Retinex multi-échelle pour l'amélioration de l'image couleur .Proceedings de la Conférence internationale 2008 sur Wavelet Analyse et reconnaissance de formes, Hong Kong, 2008: 30-31.

Fu Xueyang, Sun Ye, liwang Minghui, et al.A nouvelle approche basée sur l'image pour Retinex enhencement avec réglage d'éclairage 0,2014 IEEE Conférence internationale sur Acoustic, Speech and Signal Processing, 2014: 1190-1194.

BAILEY D G.Effcient mise en uvre de filtres morphologiques échelle de gris Conférence sur le terrain .International Programmalle Technology.2010: 421-424.

conception basée sur la plate-forme SEDCOLE P.Reconfigurable dans les FPGA pour le traitement d'images vidéo .Deparment de génie électrique et électronique, l'Imperial College, Londres, UK.2006.

Yao Aihong, Li Ling, Sun Mengzhe.Design de pipeline basé multiplicateur sur l'algorithme de stand modifié et l'arbre wallace .Advanced Researon commerce électronique, Web Application et Conférence CommunicationInternational, ECWAC 2011 Guangzhou, Chine, 2011, Partie I.

Jagadeshwar Rao M, DUBEY S.Un haut débit et un espace stand efficace multiplicateur recodé arbre wallace pour les circuits arithmétiques rapides .2012Asia Pacifique sur la recherche de troisičme cycle en électronique et microélectronique, 2012.

HENSLEY J, LASTRA A, SINGH M.Un évolutive contre-courant-asynchrone en pipeline multiplicateur de cabine radix-4 .International Symposium sur les circuits et systčmes asynchrones, 2005: 128-137.

Xu Xin, Chen Qiang, Pheng Ann Heng, et al.A méthode d'amélioration d'image rapide halofree basée sur Retinex .Journal des graphiques de conception assistée par ordinateur et par ordinateur, 2008,20 (10).

Leverick G, WU C, Szturm T.Coarse quantification dans les calculs de mesures d'entropie pour les séries chronologiques expérimental .Nonlinear Dynamics, 2014,79 (1): 93-100.

avantages de l'adhésion AET de fin d'année!