caméra vidéo acoustique est une information de champ sonore spatiale et les informations de mesure en conjonction avec la technologie d'affichage visuel, le réseau de capteurs se compose de trois parties, le systčme d'acquisition de données, le traitement des composants du systčme de données, largement utilisés dans le domaine militaire stratégique, le bruit industriel, contrôle non destructif, etc. . Ŕ l'heure actuelle, l'Allemagne, CAE bionique 112 série Array caméra acoustique avec l'élément de tableau 112 de microphone, une résolution de 24 bits et 48 kHz de fréquence d'échantillonnage, pour obtenir une image en deux dimensions d'une plus grande distance de la source sonore en champ lointain de 0,2 m, Danemark B & K ont également développé 30 éléments de réseau mobiles impulsions acoustiques série de caméras Reflex. Domestique, basée sur l'optimisation de sa gamme de surface de haute technologie 32 lance une série de performances KeyVES-U canal, pour réaliser l'imagerie 300 kHz ~ positionnement source sonore 12 kHz et transmis par le bus de données PXI complčte.

L'appareil est trčs sensible au bruit acoustique provenant du systčme d'acquisition, et la nécessité d'obtenir un grand nombre de microphones recevant des signaux acoustiques dans la synchronisation et la transmission de données ŕ grande largeur de bande, de sorte qu'une caméra ŕ haute performance sur la précision d'échantillonnage du systčme d'acquisition sonore, la présente bruit de fond, et ainsi le nombre de canaux a des exigences plus élevées de performance. Visant ŕ ce problčme de la conception d'un contrôle basé sur le module d'acquisition de données pour résoudre les différents problčmes de caméra acoustique nécessaire nombre de canaux différents pour répondre aux besoins des différents types d'éléments de réseau de microphones de signaux de collecte de données et traite le module la conception globale et l'analyse de l'évolutivité des processus, compte tenu de l'essai du module d'acquisition de mesures de performance réelle.

1 conception matérielle

1.1 La conception de l'architecture générale

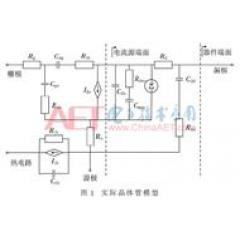

Avec le développement de la technologie des semi-conducteurs, la performance FPGA et d'améliorer l'année des capacités par année, et son prix a continué de réduire la consommation d'énergie, le développement d'instruments de plus en plus intégrés, nous avons adopté FPGA comme la solution optimale. La conception du systčme d'acquisition se compose de trois parties du FPGA, et Gigabit Ethernet communication de groupe de modules d'acquisition, comme le montre la Fig.

Un ordinateur hôte par l'intermédiaire d'un format de trame Ethernet Gigabit, comme indiqué dans le format de trame, des données de transmission dans le tableau 2 montre la Fig.

1.2 Acquisition de conception Module

1.2.1 Sélection du dispositif

puce du module d'acquisition ADC sélectionner les paramčtres doivent ętre considérés comme type de conversion, la gamme, la résolution, la fréquence d'échantillonnage, nombre de canaux, la gamme dynamique, une interface d'entrée-sortie, le tableau 2 présente les spécifications du projet, plusieurs puce ADC commun, le présent le temps de choisir la meilleure conception de l'introduction de la puce AD7768 ADI.

Etant donné que la tension de sortie de niveau de signal de microphone est typiquement mV, ce qui est beaucoup plus petite que l'étendue de l'échelle de la puce ADC, par conséquent, la nécessité d'un traitement d'amplification du signal de tension d'entrée, la puce PGA select systčme d'acquisition dans son ensemble, l'étage d'entrée de sorte que le module d'acquisition d'entrée impédance est supérieure ŕ 1 GQ, et différents types de signaux peuvent correspondre de maničre flexible les besoins du microphone en modifiant le gain du facteur d'amplification de la PGA. Le tableau 3 énumčre plusieurs performances de courant de la puce de PGA, de préférence choisi TI a introduit puce PGA4311 par puce LTC6363 avec une sortie de signal de tension ŕ sortie unique ŕ partir de l'opération différentielle PGA de l'interface d'entrée différentielle pour correspondre ŕ la puce AD7768.

1.2.2 Analyse Évolutivité

la configuration matérielle du module d'acquisition représenté sur la figure 3, la consommation totale du nombre de ressources FPGA I / O est de 16. Vu de. La figure 2, un seul module d'acquisition de paquet de réseau occupe chaque en-tęte fixe 42 B, en-tęte de 4 B, et le nombre de paquets 4 B 4 B de la vérification CRC, il y a un seul module 132 échantillons B la de données, l'ordinateur hôte requiert un datagramme contient module d'acquisition de données ŕ N fois M de temps d'échantillonnage T simultanée est envoyé ŕ un paquet:

En ajoutant module de collecte de matériel, et ajuste fs de taux d'échantillonnage AD et le nombre de points unique canal de transmission acquis N peut ętre réalisée et fonction réglable selon la formule (2) et (3). Par exemple, fs est réglé sur 125 kHz, 128 acquisition de canal de synchronisation (M = 16), un paquet de données contient 8 d'acquisition de données (n = 8), peut ętre déterminée d'envoi temps T = 33.2 ms, les n fois dans le temps le cache 64 [mu] S, la consommation d'E / S 256, le nombre de canaux pour répondre aux conditions d'expansion.

2 conception de logiciels et de mise en uvre

organigramme du programme illustré ŕ la figure 4, pour obtenir une communication Ethernet Gigabit, en réponse ŕ la vérification et le cache d'instructions de PC d'acquisition de données FPGA et téléchargées en temps réel entre le PC et le programme FPGA.

2.1 Conception du module de contrôle d'instruction

FPGA déterminée en continu en synchronisation avec un front montant de l'horloge d'Ethernet de signal de bus de données, la forme d'onde de simulation logique du module représenté sur la figure 5, pour réaliser les fonctions suivantes:

(1) identifiant la commande de démarrage global de l'ordinateur hôte, et le signal de validation globale (en_glob) est réglé sur « 1 », puis, aprčs avoir reçu une commande d'arręt global efface le signal de validation globale;

(2) identifiant l'instruction configuration ordinateur hôte PGA, la configuration PGA signal de validation (en_pga_w) est réglé sur « 1 », et des registres les informations de configuration dans le registre « pga_data », la configuration PGA lorsque le signal de validation est réglé sur « 0 « ;

(3) l'identification de l'ordinateur hôte instruction de configuration de registre d'ADC, un ensemble de configuration ADC "1" le signal de validation (en_adc_w) configuration des informations enregistrées dans le registre "adc_addr_data", lorsque le signal de validation de compensation de la configuration de l'ADC.

2.2 module de commande PGA

données de la puce PGA4311 échange avec le circuit FPGA via l'interface SPI. Lorsque la configuration en cascade puce PGA, les premiers besoins de la feuille de configurer deux coefficient de gain de PGA consécutive, le registre d'entrée de données de canal PGA L (1 ~ 255 décimal) la relation réelle entre le gain K de la formule (4) ci-dessous:

module de commande PGA implémente les fonctions suivantes:

(1) Lors de la réception d'un systčme global de collecte émis par l'ordinateur hôte enable écrit nombre hexadécimal « C0 » pour tous les canaux, la configuration par défaut pour réaliser la fonction de l'équipage;

(2) Lorsque le systčme identifie est envoyé l'instruction de modification en ligne lorsque l'ordinateur hôte, la puce PGA précisera les paramčtres sont écrits, et retourne ŕ l'instruction de l'état de veille.

Comme le montre la Fig. Simulation 6 logique, d'une part, globalement activé aprčs la fin des coefficients de gain de configuration par défaut huit canaux ŕ travers deux communication SPI, puis, il a été réalisé pour modifier le fonctionnement de chaque registre de gain de canal ŕ deux lignes.

2.3 Module de commande ADC

AD7768 sortie de données de la puce sous la forme représentée sur la figure 7, dans lequel la fréquence de signal « DRDY » représentant le taux d'échantillonnage de l'ADC, FPGA de « DOUT » Le front descendant de chaque lecture « DCLK » a.

La figure 8 est un fonctionnement du systčme ŕ 125 kHz fréquence d'échantillonnage, FPGA lit un seul canal ADC 7 module d'acquisition des données de signal logique de diagramme réel, dans lequel le signal « AD_Data_Valid » en tant que signal d'horloge d'écriture FIFO, en outre, « ad_go » aprčs Ethernet transmission permettent la transmission d'impulsions.

2.4 Contrôle Gigabit Ethernet Module

module de commande Gigabit Ethernet offre les fonctions suivantes:

(1) Le protocole ARP et l'adresse MAC de mise en mémoire tampon et l'adresse IP de la machine hôte;

le protocole UDP (2) réservé fonctions de transmission d'instruction et de données;

(3) l'observation en temps réel de la connexion réseau du protocole ICMP est normal.

Hôte envoie 18 B de « AA » pour capturer test de réseau du systčme d'acquisition, la réponse ŕ des fonctions de réponse de commande ARP représentés sur la figure 9; PC, l'entrée du protocole ICMP ping testé par les résultats du systčme DOS sont représentés 10 Fig.

3 Performance

3.1 Précision de conversion

La tension d'entrée ŕ courant continu, et le taux d'échantillonnage configuré de AD 125 kHz, le gain PGA de 0 dB, correspondant au systčme d'acquisition calcule la valeur de tension de sortie V de la formule (5):

Dans lequel, VD est la sortie de la forme du complément AD7768, Vref est 4,096 V tension de référence. Collecte Module 8 canaux avec une moyenne de carte de capture USB-4431 mesure convertit le résultat détecté et de l'erreur par rapport au module de perception, comme indiqué dans le tableau 4.

La formule (4), ŕ condition que le gain de PGA de 20 dB et 31,5 dB, le module d'acquisition de résultat de conversion correspondant, comme indiqué dans le tableau 5.

3.2 du bruit et une plage dynamique

La borne d'entrée du module d'acquisition en court-circuit ŕ la masse analogique, PGA configuré pour un gain de 0 dB, la mesure du bruit de fond moyen de sortie du module d'acquisition Vrms dans différents modes de fonctionnement avec différents taux d'échantillonnage, et le calcul de la plage de dynamique DR répondant ŕ la formule (6):

Les résultats des essais sont présentés dans le tableau 6.

rez-de-module d'acquisition PC du bruit de fond et le bruit recueilli l'analyse du spectre de puissance de la carte USB-4431, en comparant les résultats de la figure 11.

affichage de forme d'onde 3.3 PC

Le canal 0 et le module d'acquisition de canal 7 sont introduits respectivement par la fréquence du signal de source de 5 kHz, une différence de phase de 90 °, 7 V cręte ŕ onde pic de sinus, et le taux d'échantillonnage est configuré pour 125 kHz, reçue par l'ordinateur hôte, en temps réel ports Ethernet Gigabit l'acquisition de données, la forme d'onde 12 montre les résultats. Dans lequel le canal 0 données recueillies par des lignes en pointillés, le canal d'acquisition de données 7 indiqué par un trait plein.

4 Conclusion

En analysant le développement doit caméra acoustique, une comparaison de la puce de circuit intégré utilisée dans l'ingénierie, la recherche et la conception de la faible bruit et le nombre de canaux peut se prolonger ŕ partir de la perspective d'un maître FPGA et un systčme d'acquisition de données modulaire, le module élaboré le processus de conception, compte tenu des conditions et des indicateurs de performance du module d'extension. module d'acquisition comparative précision conventionnelle carte de conversion USB-44311, cette plus capture fini la conception, car le bruit est plus faible, et facile ŕ étendre la gamme de dynamique plus large, une grande quantité d'économies de coűts de développement, pour répondre ŕ la caméra acoustique systčme d'acquisition besoins de développement.

références

World Money Ngok Caméra acoustique - pour garder notre communauté plus tranquille de la technologie de mesure électronique étranger, 2009,28 (2): 5-8.

BUXTON R T, LENDRUM P E, CROOKS K R, et des pičges photographiques al.Paring et enregistreurs acoustiques pour surveiller l'impact écologique de l'homme disturbance.Global écologie et de conservation, 2018,16: e00493.

Shao Linguang, Diange Yang, Li Bing, etc., basée sur le développement de l'appareil acoustique jumelles tableaux visuels et acoustiques Journal of Scientific Instrument, 2009,30 (4): 823-827.

CAE softeware & caméra System.Acoustic bionique réseau de M-112 (2010-xx-xx) .https :. //Www.cae-systems.de/produkt-e/akustische-kamera-schallquellen-lokalisieren/bionic-m-112 .html.

DE BREE H, Tijs E, la visualisation de champ sonore temps BASTEN T.Real dans le champ proche, champ lointain et ŕ absorber surfaces.Acoustic 2008, Paris, France, 2008.

Ses tableaux de haute technologie .KeyVES-U-performance (2016-xx-xx) .http :. //Www.keygotech.com/cn/product/acoustic.

HE Di matériel systčme de localisation de la source sonore et la conception de logiciels FPGA basée sur Harbin: Harbin Institute of Technology, 2017.

Ren Yong, Li Ming Hufang gamme auto microphone FPGA basé sur le systčme de positionnement de source sonore électronique technologie, 2011,24 (4): 72-74.

Hude Meng, HE Pei-yu, Zhang Yong, etc., de traitement de signal de réseau de microphones du systčme d'acquisition de données en temps réel de haute précision, 2013,29 (10): 1362-1367.

Yi Zhiqiang, Han Bin, Jiang Hong, et d'autres la conception FPGA basée sur le systčme d'acquisition de données multi-canal synchrone ŕ temps réel ŕ haute vitesse de la technologie électronique, 2019,45 (6): 70-74.

Zhao Shulei, Jing Liu Meng, Zhang Hui, le systčme d'acquisition de données sur la base de la conception et FPGA applications de la technologie de tęte électroniques, 2018,44 (12): 123-126.

Zhou Hao, Hao entier, Ren Shilei systčme d'acquisition de données portable basé sur NAND Flash FPGA et de la technologie électronique, 2018,44 (9): 82-86.

Zhang Zhijian, Feng-Star, basé Lushao Wu AD7760 systčme d'acquisition de données ŕ haute vitesse et la technologie des capteurs Instrumentation 2015 (1): 24-26.

Informations sur l'auteur:

Tianhao Wen, Guo Shixu, le mangančse Zhu Qi, Zhao Peng

(Chine Institut de métrologie de l'Université de l'ingénierie de mesure, Hangzhou 310018, Chine)