Li Wei

(CLP Kang Group Limited, Hangzhou 311121)

: Entreprise traditionnelle puces de mťmoire SSD utilisant un particules de mode DRAM externe (Dynamic Random Access Memory) ŗ l'adresse mťmoire flash table de mappage de traduction, non seulement le coŻt ťlevť, une grande empreinte, mais aussi besoin de concevoir des processus de protection descendante puissance complexe et alimentation de secours supplťmentaire le condensateur de maintien. Utilisation d'une nouvelle rotation de l'aimantation rťmanente caractťristiques de la puce de mťmoire et de haute densitť, haute vitesse, faible consommation d'ťnergie, le temps de conservation des donnťes est longue, les caractťristiques infiniment d'endurance, proposťe sur la base de la rotation de l'aimantation de puces de mťmoire intťgrťes solution d'architecture de contrŰleur SSD simplifie considťrablement le processus et l'alimentation de secours anormale vers le bas la conception de puces de contrŰleur, le coŻt d'ťconomie condensateur d'alimentation de secours SSD interne, capacitť de levage de soutien efficace SSD.

: Rotation puce de mťmoire magnťtique; SSD; architecture de puce; embarquť

: TN492 Code du document: ADOI: 10,19358 / j.issn.1674-7720.2017.01.009

Format de rťfťrence : Wei Li une architecture de puce de contrŰleur de disque d'ťtat solide d'une rotation de magnťtisation intťgrťe de puce de mťmoire [J] SES APPLICATIONS, 2017,36 (1) :. 2931..

0 introduction

Avec les grandes donnťes et le dťveloppement du cloud computing, une grande quantitť de besoins de donnťes ŗ stocker, d'autre part, avec les progrŤs de la mise ŗ niveau et le rendement de la technologie mťmoire flash NAND (Flash NAND), le coŻt des disques SSD (Solid State Disk, SSD) est tombť trŤs proche du niveau de classe entreprise disque dur mťcanique (disque dur), les applications SSD plus largement dans les serveurs, les centres de donnťes et les systŤmes de stockage.

contrŰleur traditionnel SSD de classe entreprise de solutions de stockage de donnťes pour la plupart sur la base et le programme d'entrťe DRAM, conÁu non seulement difficile, processus complexe coupure d'alimentation anormale, et dans le SSD nťcessitent beaucoup d'espace pour mettre les condensateurs au tantale d'alimentation de secours, non seulement d'augmenter le coŻt et limite l'utilisation de l'espace dans le disque, il ne peut pas Ítre fait pour amťliorer la capacitť du SSD.

La prťsente puce mťmoire intťgrťe gyromagnťtique (SpinTransferTorque Magnetic Random Access Memory, STTMRAM) est appliquťe ŗ l'architecture de puce contrŰleur SSD, le processus anormal peut Ítre simplifiť pour ťconomiser condensateur de secours d'alimentation au sein du SSD et peut Ítre renforcer la capacitť du disque dur de plus de 30%.

profils de programme d'architecture de contrŰleur de disque d'ťtat solide du courant 1

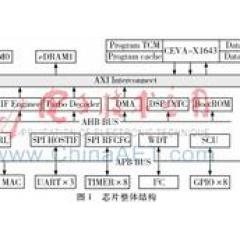

La figure 1 est un schťma de principe de l'entreprise dominante actuelle programme d'architecture SSD.

Le rťgulateur de courant SSD en plusieurs puces majeure partie du module d'interface d'hŰte, du module de gestion de systŤme, de l'extrťmitť avant de l'extrťmitť arriŤre du module d'interface flash.

L'extrťmitť avant du module d'interface d'hŰte est responsable de la rťception et de traitement dťlivrť par la commande d'ťcriture d'hŰte et les donnťes de rťception cŰtť vers le bas vers la mťmoire DRAM. Enterprise SSD en raison des exigences de haute performance, l'extrťmitť avant de l'interface hŰte est essentiellement basťe sur la sťlection d'interface de troisiŤme gťnťration PCIe NVMe (NonVolatile Memory Express) protocole (PCI Express), en plus, SAS (Serial Attached SCSI) 12 G et SATA (Serial ATA) interface est ťgalement protocole intťgrer l'interface hŰte frontal SSD.

le module de gestion de systŤme est l'unitť de base de la puce de contrŰleur SSD comprenant une table de mappage d'adresses de mťmoire flash (Flash Traduire couche, FTL) la gestion, la gestion des mťtadonnťes, la gestion des journaux, le contrŰle de processus et analogues. FTL gestion d'entrťe qui est la plus importante partie.

Une table de correspondance entre l'adresse physique (Adresse Physical Block, PBA) FTL dťlivrť par le traitement principal de l'hŰte adresse logique (adresse logique du bloc, LBA) stockťe dans les particules de milieu, est de simuler entiŤrement les opťrations de disque dur traditionnel clignotent couche de logiciel, il couche FTL du dispositif de mťmoire flash pour une utilisation, une couche de FTL efficace affecte directement les performances de l'appareil.

Effet module de gestion de systŤme comprend essentiellement les points suivants: FTL gestion d'entrťe; processus de collecte des ordures, l'espace d'alimentation supplťmentaire, procťdť d'ťchange de froid / chaud; donnťes parallťlisme plan entre le canal de puce; t‚che de tri demande; gestion tampon, la gestion des blocs dťfectueux, ťquilibrer le processus d'usure, le processus de rťcupťration de panne de courant, le processus ECC.

Interface Flash NAND est responsable du traitement des donnťes et des commandes ťchange de particule Flash NAND. NFI commande d'ťcriture ŗ partir du cŰtť de l'hŰte est responsable de la conversion soit compatible avec l'interface NAND norme ONFI bascule et le protocole, et ne lire et ťcrire des donnťes dans l'interaction entre les particules et le tampon de donnťes du contrŰleur de NAND.

disque SSD sur le circuit imprimť et la puce de contrŰleur en plus d'un grand nombre de particules Flash NAND, comprenant en outre les principaux composants suivants:

(1) plug-in particules DRAM disque SSD effet comporte deux aspects principaux: une mťmoire cache de lecture et des donnťes d'ťcriture et le plan d'accŤs FTL. Pour rťpondre ŗ cette conception de la demande, adaptťe ŗ la conception de la puce contrŰleur protocoles de DDR, le besoin de dťvelopper un PHY DDR DDR le contrŰleur et l'adaptation, de rťserver un espace supplťmentaire sur l'arrangement de circuit imprimť et le signal ŗ grande vitesse mise en page des particules de DRAM.

Effet (2) Capacitť ťlectrique (condensateur d'alimentation de secours) est de mise hors tension en cas d'accident, les particules peuvent Ítre rapidement et stockťes dans l'entrťe DRAM FTL ŗ l'appui de la capacitť d'une alimentation de secours, brosse de sol pour sŻr et rapide non volatile milieu volatil (NAND flash), pour ťviter la perte de FTL d'entrťe causťe par la perte de donnťes.

Moins que l'architecture de puce contrŰleur classique SSD est le suivant:

(1) En raison des populaires solutions de classe entreprise avec une industrie DRAM externe est de stocker les particules entrťe FTL, ce qui nťcessite des contrŰleurs DDRPHY et DDR supplťmentaire adapter ŗ l'intťrieur de la puce, la difficultť de dťvelopper contrŰleur DDR et DDR PHY est assez grande, et le coŻt de la propriťtť intellectuelle sous licence de EDA fournisseur place et trŤs coŻteux, ce qui augmente les coŻts de conception et de dťveloppement.

(2) limitant l'espace intťrieur du disque, deux pour les 2,5 pouces classiques SSD carte de circuit imprimť (PCB), comme illustrť dans le schťma de la figure. A partir d'une anatomie de disque d'entreprise de la sociťtť SSD intťrieur bien connu peut Ítre vu, disque dur carte de circuit imprimť SSD environ 80% de l'espace est plein de particules de mťdias flash, un autre 20% de l'espace mis puces de contrŰleur SSD, DRAM et particules condensateurs d'alimentation de secours.

(3) entreprise SSD pour les exigences de fiabilitť de donnťes trŤs ťlevťs, qui doivent Ítre conÁus dans une variťtť de conditions anormales (par exemple, la mise hors tension anormale), le contrŰleur peut Ítre mis ŗ l'intťrieur du contenu noyau table de -FTL stockťe dans le non-sťcurisť des supports volatils. Dans l'architecture classique puce contrŰleur SSD de classe entreprise, les magasins DRAM interne d'entrťe de FTL, donc en cas de panne de courant anormale, vous devez brosser Flash NAND ŗ la FTL DRAM dans le tableau interne. En bref, est de condensateurs d'alimentation de secours pris en charge dans ce court laps de temps, le contrŰleur peut Ítre saisie de donnťes FTL dans la mťmoire flash NAND sous la forme d'une opťration d'ťcriture. Par consťquent, la conception d'alimentation de secours, on a besoin de consommer de grandes quantitťs de condensateurs tantale CMS pour fournir l'ťnergie ťlectrique de secours, ce qui dans l'espace disponible sur le PCB sera encore rťduite, et deuxiŤmement, une alimentation de secours liťs aux donnťes de gestion des exceptions flux, le matťriel augmentera ainsi que la complexitť de la conception firmware.

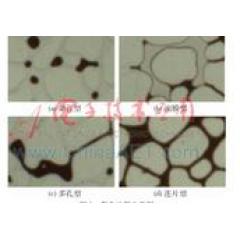

2 puce de mťmoire gyromagnťtique (STTMRAM) Caractťristiques

Parmi les nouveaux support de mťmorisation non-volatile, la puce de mťmoire de rotation de magnťtisation (STTMRAM) peut Ítre satisfaisante compatible avec le processus de semi-conducteur CMOS, en utilisant des couches moins mťtalliques qui peuvent atteindre des cellules de mťmoire intťgrťs ŗ haute densitť. En raison de sa proximitť SRAM (Static Random Access Memory, SRAM) lire et vitesses d'ťcriture, statique faible et la puissance dynamique, les caractťristiques descendantes puissance comprenant non volatile, rťinscriptible nombre presque infini de fois, ŗ une tempťrature ťlevťe pendant une longue pťriode la rťtention des donnťes et la rťsistance aux caractťristiques de rayonnement de champ magnťtique fort, en tant que contrŰleur de l'entreprise SSD intrinsŤquement bon support et l'entrťe de cache de donnťes est stockť dans FTL [1].

ņ l'heure actuelle, de nombreux fabricants semi-conducteurs vont concevoir la prochaine gťnťration de puce MRAM non volatile support de stockage mise au point R & D, en plus de TSMC, Samsung et Toshiba ont continuť ŗ promouvoir le dťveloppement de STTMRAM en dehors des …tats-Unis EVERSPIN sociťtť a publiť 256 MB puce de test de production de masse. Gr‚ce ŗ l'amťlioration et l'avancement du rendement du procťdť, la STTMRAM d'application dans le segment de zone de stockage sera plus ťtendue [2].

applications STT-MRAM intťgrťs dans l'architecture de puce contrŰleur SSD, la pleine utilisation de sa puissance vers le bas caractťristiques de donnťes non volatiles, peuvent ťconomiser beaucoup d'alimentation de secours et les processus de conception d'alimentation de secours, ce qui simplifie grandement la conception de l'architecture du contrŰleur SSD. De plus, puisque les ťconomies des condensateurs au tantale SMD, le PCB peut Ítre pris en charge la place de plus d'espace plus de particules NAND Flash, pour atteindre une plus grande capacitť. En outre, pour simplifier la conception de la puce de contrŰleur IP interne dťpendant Interface DDR, en utilisant l'interface de bus interne de STTMRAM intťgrť (SRAMlike), simplifie la conception et la difficultť de rťduire les traces de sociťtť de latence de signal impact sur les interfaces de signaux ŗ grande vitesse afin d'ťviter.

3 solutions d'architecture de contrŰleur SSD basť sur le stockage embarquť du spin magnťtique

3 est une vue schťmatique de l'architecture de la puce de contrŰleur SSD intťgrť aprŤs l'application STTMRAM.

Caractťristiques techniques de cette approche sont les suivants:

(1) enlever le dispositif de commande puce contrŰleur SSD DDR et DDR PHY, interface SRAM (SRAMlike) sur la base directement sous la forme d'une puce de contrŰleur embarquť intťgrť dans STTMRAM.

SRAMlike puce d'interface de bus signal de sťlection comprend CS, de validation d'ťcriture WE, une validation de lecture RE, une sortie signal de validation OE, une remise ŗ zťro RST, horloge CLK, des lignes d'adresse A [31: 0], les lignes d'entrťe de donnťes DIN [31: 0] et la ligne de sortie de donnťes DOUT [31: 0]. Utilisation du module d'interface de bus interne coopŤre avec le dispositif de commande interne, les lignes de signal peut Ítre considťrablement rťduit et le retard de transmission provoquť par un protocole d'interface de tÍte externe, afin d'amťliorer encore les performances du dispositif de commande.

(2) se situe de rŰle principal dans STT-MRAM: ťmis par le rťcepteur de donnťes interface hŰte frontal, l'extrťmitť arriŤre du tampon de donnťes comme interface flash; entrťe de la table de la couche de traduction de mťmoire flash; stocker les mťtadonnťes, telles que le nombre de pages valides, les blocs dťfectueux gestion de l'information, le micrologiciel, le code de dťmarrage, et de la matrice de contrŰle si rares.

(3) simplifier le processus d'alimentation de secours. Dans le dispositif de commande d'architecture de puce classique de SSD, ťtant donnť que les donnťes et les entrťes FTL sont stockťes dans la DRAM, et donc pour assurer la fiabilitť des donnťes rencontrťes dans le cas d'une mťmoire DRAM ayant une puissance vers le bas des propriťtťs de bas puissance anormale des donnťes volatiles, , dans la puce du contrŰleur classique nťcessite plaque de charge condensateur d'alimentation de secours support de flash lance une opťration d'ťcriture devra enregistrer des informations importantes ŗ tous de la brosse dans la mťmoire flash non volatile, la prochaine fois que la puissance, le contrŰleur requis FTL dťclenche une opťration de lecture, puis re-lire l'entrťe des donnťes dans la DRAM et analogues, l'achŤvement de l'initialisation du systŤme. La figure 4 est un organigramme bas SSD de puissance anormale.

Dans le cadre du prťsent mode de rťalisation, ťtant donnť que les caractťristiques non-coupure d'alimentation de STTMRAM intťgrť, rencontrť lors d'une mise hors tension anormale, et les donnťes peuvent encore entrťes FTL organigramme de la figure 4SSD puissance anormale vers le bas pour stocker en toute sťcuritť, le systŤme flux d'alimentation de secours sera grandement simplifiťe. disque Tantale utilisť pour l'alimentation de secours interne peut ťgalement Ítre retirť, ťconomiser le coŻt de la conception matťrielle de l'intťrieur du disque. Vous pouvez voir l'analyse anatomique basťe sur le disque SSD de classe entreprise de 900 Go d'une interface SAS, afin de rťpondre aux besoins d'alimentation de secours, le PCB disque total placť un total de plus de 400 condensateurs au tantale. Si l'architecture du prťsent mode de rťalisation, ces plus possible de supprimer tous les condensateurs au tantale, d'ťconomiser sur le coŻt des composants matťriels, d'autre part, l'utilisation de la zone de PCB pour enlever le tantale coller des particules Flash NAND, au moins possible d'amťliorer la capacitť du SSD 20%.

4 Conclusion

Papier, basť sur l'architecture du contrŰleur embarquť STTMRAM SSD, il est possible de simplifier considťrablement le rťgulateur de dťbit d'alimentation de secours FTL ŗ l'entrťe, pour simplifier la difficultť de conception et coŻt disque PCB, lire et les performances d'ťcriture de la levťe de SSD et peut soutenir efficacement le SSD pour atteindre une plus grande capacitť. Avec la mise ŗ niveau d'avancement de la technologie et le rendement STTMRAM, des puces de mťmoire de spin magnťtique seront largement appliquťes dans le domaine de plus segment de stockage.

rťfťrences

[1] TANG D D, LEE Y J. fondamentaux de mťmoire magnťtique et de la technologie [M] Angleterre :. Cambridge University Press, 2010.

[2] Xie Yuan technologies de mťmoire ťmergentes :. Conception, architecture et applications [M] Allemagne :. Springer, 2014.