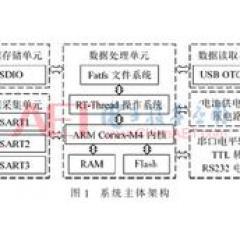

Prenant la parole sur l'article est, adresse E / S espace est un espace trŤs limitť (64KB), il est gťnťralement dans l'espace E / S dans les deux deux registres, les points d'adresse interne ŗ la premiŤre opťration, le deuxiŤme stockage lire ou donnťes d'ťcriture. Ainsi, pour les cycles de configuration PCI, les deux ťtapes comprenant:

Etape 1: Adresse CPU de la premiŤre IO Adresse 0xcf8 ~ 0xCFB la opťration d'ťcriture sur les registres de configuration. Comme cela est reprťsentť ci-dessous, qui comprend le numťro de bus (Nombre Bus), le numťro de dispositif (Device Number), le numťro de fonction (numťro de fonction) et un pointeur registre.

Etape 2: Lire ou donnťes d'ťcriture ŗ la CPU ťcrit l'adresse IO dans 0xCFC ~ 0xCFF.

Rappelons que chaque fonction de PCI (Fonction) contient 256 octets d'espace de configuration (configuration spatiale), qui est dťsignť sous le nom 64 premiers octets en-tÍte, les 192 octets restants sont utilisťs pour un certain nombre de caractťristiques facultatives. PCI Spec prťvoit deux types d'en-tÍte: Type1 et Type0. Dans lequel, Type1-tÍte indique la fonction pťriphťrique pont PCI (Brige), tandis que Type0 en-tÍte indique le fonctionnement de l'appareil ne sont pas pont PCI. vues d'en-tÍte de deux structures sont les suivantes:

Remarque: Le PCIe complet a hťritť l'en-tÍte PCI contenu pertinent, donc une description dťtaillťe de l'en-tÍte et des opťrations sera remise sur l'introduction de PCIe.